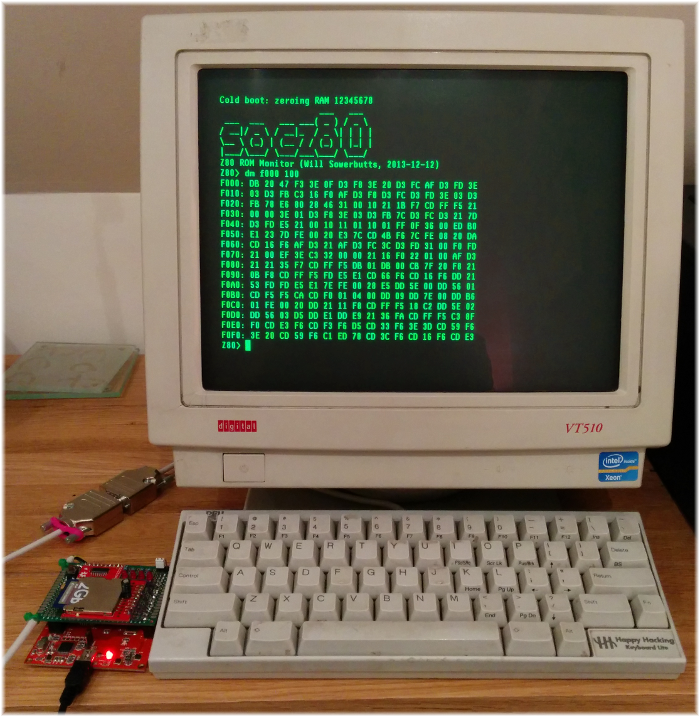

Will Sowerbutts designed a system which includes a Z80 and a caching SDRAM controller - and it's all open source.

Quote:

[Will] wrote a 128MHz Z80-based retro microcomputer which runs on a Papilio Pro board (built around a Spartan-6 LX9 FPGA.) The T80 CPU core was taken from opencores, the SDRAM controller from Mike Field’s work and [Will] implemented additional functions:

– a 4KB paged Memory Management Unit to translate the 16-bit (64KB) logical address space into a 26-bit (64MB) physical address space.

– a 16KB direct mapped cache to hide the SDRAM latency, using the FPGA internal block RAM

– a UART interface for external communications

He also ported CP/M-2.2, MP/M-II and UZI (a UNIX system) to the computer. His project is completely open-source and all the source code can be downloaded at the end of [Will]’s write up.

– a 4KB paged Memory Management Unit to translate the 16-bit (64KB) logical address space into a 26-bit (64MB) physical address space.

– a 16KB direct mapped cache to hide the SDRAM latency, using the FPGA internal block RAM

– a UART interface for external communications

He also ported CP/M-2.2, MP/M-II and UZI (a UNIX system) to the computer. His project is completely open-source and all the source code can be downloaded at the end of [Will]’s write up.

via the FPGA ATOM topic on stardot.

The base SDRAM controller can be seen here but for me the cache is the interesting part.