Hi,

the

Studio 68 is a board to make retrocomputing "experiments" with old CPU.

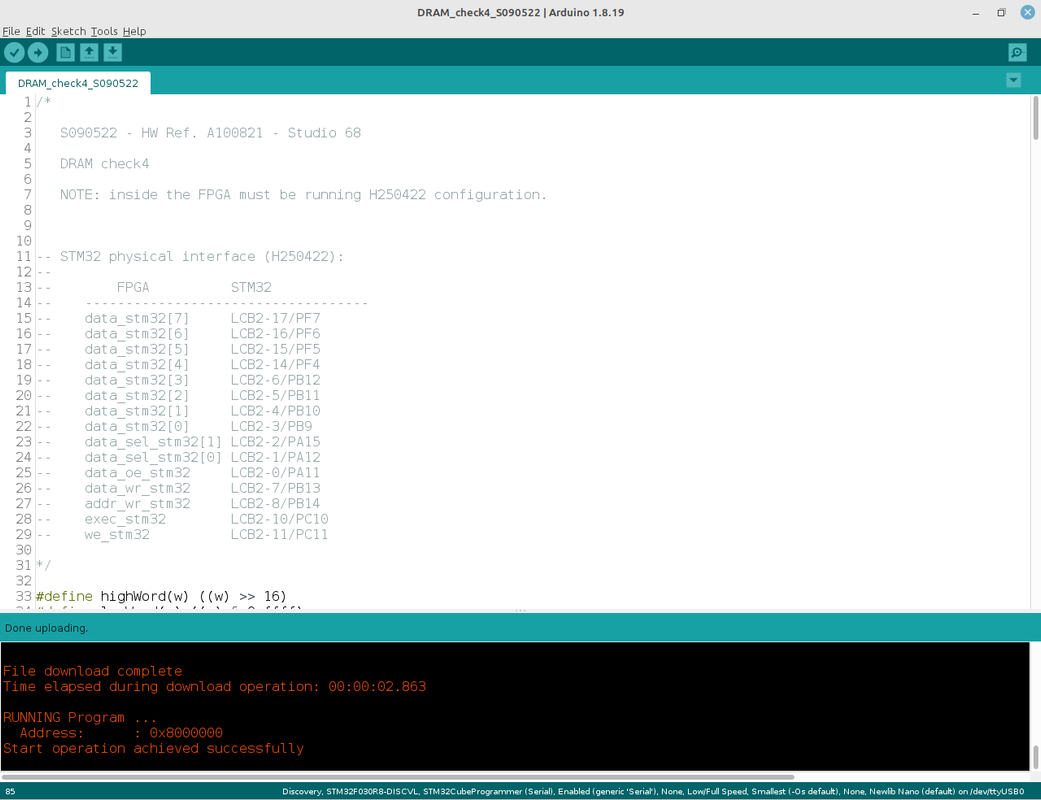

It is an FPGA-centric design so all (or most) of the control logic and I/O can be synthesized inside the FPGA (as a configurable chip set). There is also a STM32 MCU that can be used as "companion processor" (i.e for I/O or boot).

The STM32 can be programmed with the Arduino IDE (with the STM32 "core") as the STM32 section of the board is compatible with the

ST Discovery Board with the same MCU.

On board there is also a 68SEC000 CPU just to start playing with it.

More, an external bus with 5V translators allows to add external "Application Boards" with others CPU (putting the internal 68SEC000 CPU in High-Z).

The external bus is completely configurable by the FPGA so it is virtually HW independent.

Here the block diagram:

Attachment:

Studio 68 Blocks.jpg

Here the board (4-layers PCB):

Attachment:

Studio 68_Front.jpg

Attachment:

Studio 68_Back.jpg

and here a first test running the 68SEC000 CPU (all the control and I/O logic is synthesized inside the FPGA, and the STM32 is used as FPGA-serial bridge):

Attachment:

Hello Studio 68.jpg

The next step will be to test the external bus with an "Application Board" with a KR1802VM2 CPU, a Soviet PDP11 clone.

The KR1802VM2 CPU has a fully static design and the clock can be 0Hz, so it can easily connected to a 5V MCU for single clock pulses testing.

So I've done as first step a test board (a "shield" for my development board

PicOne) to check some behaviors of this CPU (and of course check if it works

) before making the Application Board add-on for the Studio 68, and it's currently on the way...: